绝缘栅场效应晶体管

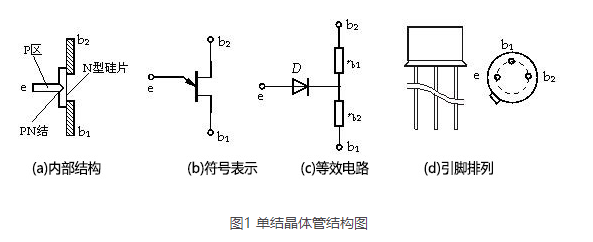

SiO 2的表面和两个N型区域分别称为源极s,栅极g和漏极d。在其图形表示法中,箭头表示漏极电流的实际方向。

绝缘栅场效应晶体管的导电机制是通过使用UGS来控制漏电流ID以控制“感应电荷”。改变导电通道的宽度。

如果UGS = 0,则存在增强的MOS晶体管,在源极和漏极之间没有导电沟道。当UGS = 0时,存在耗尽MOS晶体管,在漏极和源极之间具有导电沟道。

在图2中,衬底是P型半导体,其顶部是SiO2膜,SiO2膜覆盖有金属铝层。如果在金属铝层和半导体之间施加电压UGS,则金属铝和半导体是垂直于半导体表面产生的电场。

在该电场下,P型硅表面上的多数载流子被排斥,导致在硅晶片表面上缺少载流子的薄层。同时,在电场作用下,P型半导体中的少数载流子 - 电子被吸引到半导体表面,被空穴捕获形成负离子,形成不可移动的空间电荷层(称为耗尽层,也称为受体)。

离子层)。 UGS越大,电场排斥硅表面层中的空穴越多,耗尽层越宽,UGS越大,电场越强;当UGS增加到某个栅极源极电压值VT(称为阈值电压或导通)时,在电压下,电场在排斥半导体表面层的多数载流子空穴形成耗尽层后吸引少数载流子 - 电子,并且然后在表面层中形成电子累积,从而使空间变空。

大多数P型半导体的表面形成N型薄层。由于它与P型衬底的导电类型相反,因此称为反型层。

在反转层下面是由负离子组成的耗尽层。 N型电子层连接最初由PN结的高电阻层隔开的源区和漏区,以形成导电沟道。

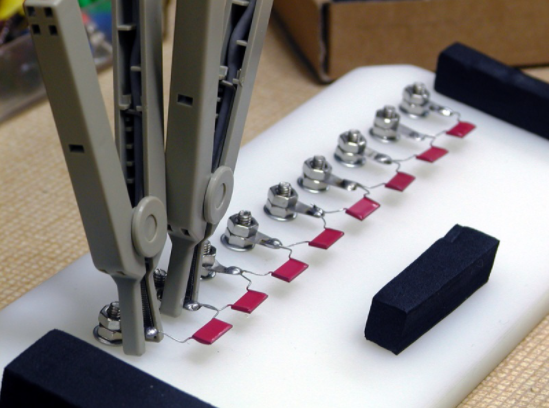

使用图2所示电路分析栅极 - 源极电压UGS以控制导电沟道的宽度并改变漏极电流ID的关系:当UGS = 0时,由于没有电场,导电沟道无法形成即使排水源是外部连接的。有ED电源,但由于漏极和源极被P型衬底隔开,漏极和源极之间有两个PN结,因此只有很小的反向电流可以流过,ID≈0;当UGS> 0并且逐渐增加到VT时,反转层开始形成,漏极源通过N通道连接。

这时,在正漏极 - 源极电压UDS的作用下; N沟道中的多子(电子)产生漂移运动,并从源极流到漏极以形成漏极电流ID。显然,UGS越高,电场越强,在表面上感应的电子越多,N通道越宽,通道电阻越小,并且ID越大。

Idss - 饱和漏极电流。它指的是结或耗尽绝缘栅场效应晶体管中栅极电压UGS = 0时的漏源电流。

向上 - 夹断电压。它指的是当漏极源刚刚关闭时,结或耗尽型绝缘栅场效应晶体管中的栅极电压。

Ut - 打开电压。当漏极和源极刚刚导通时,指增强型绝缘栅场效应晶体管中的栅极电压。

gM - 跨导。栅极 - 源极电压UGS-控制漏极电流ID的能力,即漏极电流ID的变化量与栅极 - 源极电压UGS的变化量的比率。

gM是测量FET放大的重要参数。 BVDS - 漏源击穿电压。

它指的是当栅极 - 源极电压UGS恒定时FET可以承受的最大漏极 - 源极电压。这是一个限制参数,施加到FET的工作电压必须小于BVDS。

PDSM - 最大耗散功率。它是一个限制参数,指的是FET性能不会恶化时允许的最大漏源功耗。

使用时,FET的实际功耗应小于PDSM并留有一定的余量。 IDSM - 最大漏极电流。

它是一个限制参数,指的是FET正常工作时漏极和源极之间允许的最大电流。 FET的工作电流不应超过IDSM。